# A-level COMPUTER SCIENCE

Paper 2

7517/2

## Insert

FIGURE 1 for use in answering Question 4

FIGURE 3 for use in answering Question 5

**TABLE 1 for use in answering Question 6**

FIGURE 4 for use in answering Question 6

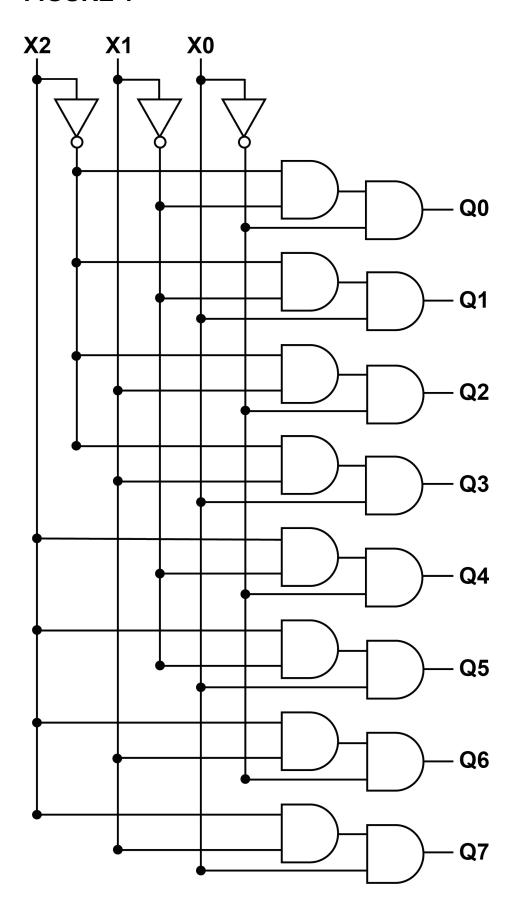

FIGURE 1

# FIGURE 3

Facility(FacilityID, Description, MaxPeople, PricePerHour)

FacilityForSport(Sport, FacilityID)

Booking(FacilityID, BookingDate, StartTime, EndTime, CustomerID)

Customer(CustomerID, Forename, Surname, EmailAddress)

TABLE 1

Standard AQA assembly language instruction set

| LDR Rd,                          | Load the value stored in the                              |

|----------------------------------|-----------------------------------------------------------|

| <memory ref=""></memory>         | memory location specified by                              |

|                                  | <pre><memory ref=""> into register d.</memory></pre>      |

| STR Rd,                          | Store the value that is in register d                     |

| <memory ref=""></memory>         | into the memory location specified                        |

|                                  | <pre>by <memory ref="">.</memory></pre>                   |

| ADD Rd, Rn,                      | Add the value specified in                                |

| <pre><operand2></operand2></pre> | <pre><operand2> to the value in register</operand2></pre> |

|                                  | n and store the result in register d.                     |

| SUB Rd, Rn,                      | Subtract the value specified by                           |

| <pre><operand2></operand2></pre> | <pre><operand2> from the value in</operand2></pre>        |

|                                  | register n and store the result in                        |

|                                  | register d.                                               |

| MOV Rd,                          | Copy the value specified by                               |

| <operand2></operand2>            | <pre><operand2> into register d.</operand2></pre>         |

| CMP Rn,                          | Compare the value stored in                               |

| <pre><operand2></operand2></pre> | register n with the value specified                       |

|                                  | <b>by</b> <operand2>.</operand2>                          |

| B <label></label>                | Always branch to the instruction at                       |

|                                  | position <label> in the program.</label>                  |

| B <condition></condition>        | Branch to the instruction at                              |

| <label></label>                  | position <label> if the last</label>                      |

|                                  | comparison met the criterion                              |

|                                  | <pre>specified by <condition>.</condition></pre>          |

|                                  | Possible values for <condition></condition>               |

|                                  | and their meanings are:                                   |

|                                  | EQ: equal to NE: not equal to                             |

|                                  | GT: greater than LT: less than                            |

5

| AND Rd, Rn,                      | Porform a hitwise logical AND                                                |

|----------------------------------|------------------------------------------------------------------------------|

| <pre><operand2></operand2></pre> | Perform a bitwise logical AND                                                |

| <pre><pre></pre></pre>           | operation between the value in                                               |

|                                  | register n and the value specified                                           |

|                                  | by <pre>coperand2&gt; and store the</pre>                                    |

|                                  | result in register d.                                                        |

| ORR Rd, Rn,                      | Perform a bitwise logical OR                                                 |

| <operand2></operand2>            | operation between the value in                                               |

|                                  | register n and the value specified                                           |

|                                  | by <pre><pre>by <pre><pre>operand2&gt; and store the</pre></pre></pre></pre> |

|                                  | result in register d.                                                        |

| EOR Rd, Rn,                      | Perform a bitwise logical XOR                                                |

| <operand2></operand2>            | (exclusive or) operation between                                             |

|                                  | the value in register n and the                                              |

|                                  | value specified by <pre><pre>operand2&gt; and</pre></pre>                    |

|                                  | store the result in register d.                                              |

| MVN Rd,                          | Perform a bitwise logical NOT                                                |

| <operand2></operand2>            | operation on the value specified by                                          |

|                                  | <pre><operand2> and store the result in</operand2></pre>                     |

|                                  | register d.                                                                  |

| LSL Rd, Rn,                      | Logically shift left the value stored                                        |

| <operand2></operand2>            | in register n by the number of bits                                          |

|                                  | specified by <pre><pre>operand2&gt; and store</pre></pre>                    |

|                                  | the result in register d.                                                    |

| LSR Rd, Rn,                      | Logically shift right the value                                              |

| <pre><operand2></operand2></pre> | stored in register n by the number                                           |

|                                  | of bits specified by <pre><pre>operand2&gt;</pre></pre>                      |

|                                  | and store the result in register d.                                          |

| HALT                             | Stops the execution of the                                                   |

|                                  | program.                                                                     |

# **BLANK PAGE**

LABELS: A label is placed in the code by writing an identifier followed by a colon (:). To refer to a label, the identifier of the label is placed after the branch instruction.

### Interpretation of <operand2>

<operand2> can be interpreted in two different ways,

depending on whether the first character is a # or an R:

- # use the decimal value specified after the #, eg

#25 means use the decimal value 25

- Rm use the value stored in register m, eg R6 means use the value stored in register 6

The available general-purpose registers that the programmer can use are numbered 0–12

#### FIGURE 4

```

CMP R2, #0

BEO exit

MOV RO, #0

MOV R3, #1

moveleft:

LSL R2, R2, #1

LSL R3, R3, #1

CMP R2, R1

BLT moveleft

BEQ mainloop

LSR R2, R2, #1

LSR R3, R3, #1

mainloop:

CMP R1, R2

BLT skip

ADD R0, R0, R3

SUB R1, R1, R2

skip:

AND R4, R3, #1

CMP R4, #1

BEQ skipshiftR2

LSR R2, R2, #1

skipshiftR2:

LSR R3, R3, #1

CMP R3, #0

BNE mainloop

exit:

HALT

```

### **END OF SOURCE MATERIAL**

# **BLANK PAGE**

#### **BLANK PAGE**

#### **Copyright information**

For confidentiality purposes, all acknowledgements of third-party copyright material are published in a separate booklet. This booklet is published after each live examination series and is available for free download from www.aqa.org.uk.

Permission to reproduce all copyright material has been applied for. In some cases, efforts to contact copyright-holders may have been unsuccessful and AQA will be happy to rectify any omissions of acknowledgements. If you have any queries please contact the Copyright Team.

Copyright © 2021 AQA and its licensors. All rights reserved.

#### IB/M/CD/Jun21/7517/2/E3